| Fakulti:FAKULTI KEJURUTERAAN ELEKTRIK  |                  |                                 |  |  |  |

|----------------------------------------|------------------|---------------------------------|--|--|--|

|                                        | Semakan          | :1                              |  |  |  |

| Nama Matapelajaran: MAKMAL PBL TAHUN 3 | Tarikh Keluaran  | : 2020                          |  |  |  |

| Kod Matapelajaran : SKEL 3742          | Pindaan Terakhir | : <del>-2020</del> 5th May 2020 |  |  |  |

|                                        | No. Prosedur     | : PK-UTM-FKE-(0)-10             |  |  |  |

SKEL 3742

# SEKOLAH KEJURUTERAAN ELEKTRIK UNIVERSITI TEKNOLOGI MALAYSIA KAMPUS SKUDAI JOHOR

# VLSI SYSTEM DESIGN LABORATORY (VLSI DESIGN)

# **Pre-Lab : IC Design Flow**

| Prepared by                | :                                      | Certified by | :                                     |

|----------------------------|----------------------------------------|--------------|---------------------------------------|

| Mr. Izam bin<br>Dr. Muhamm | Kamisian<br>ad Afiq Nurudin bin Hamzah |              | ubita binti Sudirman<br>E Department) |

| Dr. Shahidatu              | l Sadiah binti Abdul Manan             |              |                                       |

| Signature                  | :                                      | Signature    | :                                     |

| Stamp                      | :                                      | Stamp        | :                                     |

| Date                       | : 9 February 2020                      | Date         | : 9 February 2020                     |

# Task

In this lab, we will be using four Synopsys tools to design an integrated circuit (IC), which are:

- 1. Verilog Compiler and Simulator (VCS) for circuit design verification.

- 2. Design compiler (DC) for synthesis.

- 3. IC Compiler (ICC) for place and route.

- 4. Prime Time (PT) for static timing analysis (STA).

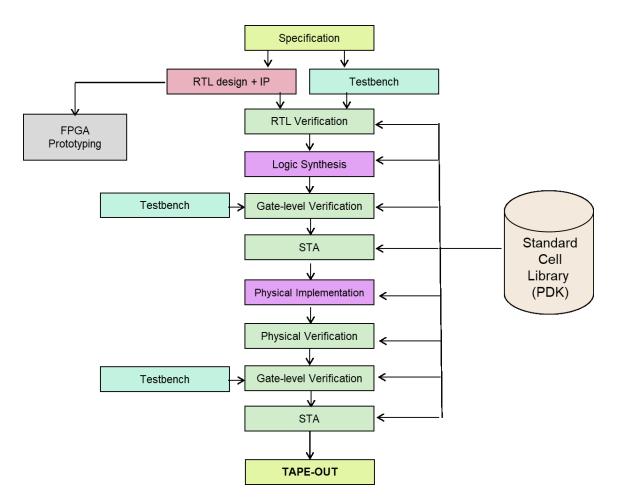

The complete design flow is shown in Figure 1 below:

Figure 1: Complete IC Design Flow

For prelab, you are required to go through the tasks for all four tools before coming to the in-lab session and submit the answers for all the questions in the first lab session.

# Verification Lab

# Task 1

In this lab, you will run a basic verilog simulation using Synopsys VCS. This simulation exercise will use VCS's graphical user interface tool called DVE. The design used is a simple 4-bit adder.

Go to directory task1

# cd ~/lab\_work/verification/task1

Use the "Is" command to view the files in this directory. You should find two files: adder.v (design file) and test\_adder.v (testbench file)

Run VCS to check if your verilog files have any syntax errors:

# vcs adder.v

On your screen, you will see the VCS copyright information, followed by various compile log information. Look for the message that says "../simv is up to date":

```

-lm -lpthread -ldl

../simv up to date

CPU time: 1.738 seconds to compile + .436 seconds to elab + .612 seconds to link

```

This indicates your design does not have any syntax errors and is ready for simulation.

Now lets check the testbench. Since the testbench instantiates the adder, we need to compile both files:

# vcs test\_adder.v adder.v

Did you get the message "../simv is up to date", if yes, then both files have no syntax errors. We will see how to fix syntax errors in the next lab. For now, lets run the simulation. To simulate the design:

# vcs -R -gui -debug\_all test\_adder.v adder.v

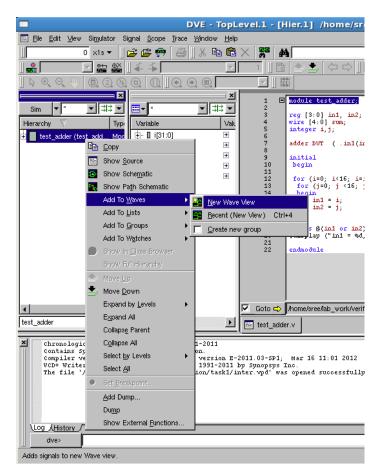

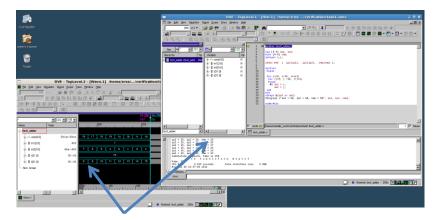

The "-R" option tells VCS to run the simulation after compilation, while the "-gui" option invokes DVE, the graphical interface. The debug\_all option allows for source tracing. Wait for DVE gui to appear. You will get the following window:

| DVE - TopLevel.1 - [Sour                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | e.1 - test_adder: test_adder.v] /home/sree//verification/task1/simv |       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-------|

| 🔄 File Edit View Simulator Signal Scope Trace Window He                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                     | _ @ × |

| 0 x1s 🔻 🛛 😂 🍘 🎒 🕺 🖓 🛍 🕻                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                     |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | → → _ → _ →                                                         | 1 🏵 🔻 |

| ] \ @ @ @ @ @ @ @ @ @ @ ■                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                     |       |

| Sm         ▼         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★         ★ | <pre></pre>                                                         |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Goto C // home/sree/tab_work/verification/task1/test_adder.v 1      | Reuse |

| test_adder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | test_adder.v                                                        |       |

| Comparison of a semilator complete 1917-001<br>contails company projectory formation<br>contails company projectory formation<br>to the file ("Jones/scee/lab_work/we filestan/tast/<br>The file ("Jones/scee/lab_work/we filestan/tast/<br>Uog Arbstow /                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | bu Sunousus Inc.                                                    |       |

| dve>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                     |       |

| <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ⇒ stopped: 0s 🖽 🖬 🖬                                                 |       |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                     |       |

Right click on the Testbench module (test\_adder) under the hierarchy pane, and select **Add to Waves - New Wave View** as in the figure below.

This will launch the waveform viewer, and load all the signals (ports, signals) into it. There is no waveform value yet, as the simulation has not been run.

Run the simulation by clicking on the RUN button

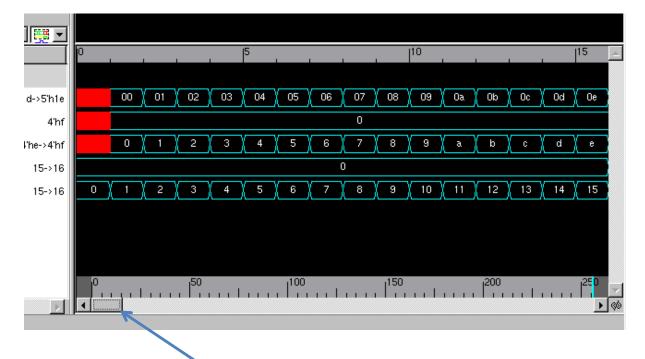

You can click on the run button on either the waveform window or the main DVE gui - both perform the same operation. This action will cause the simulation to run until completion. You will see the waveform displayed on the wave window.

Use the zoom in button on the toolbar to get a closer look. **Click** on the **zoom in button** a few times.

2 c zoom out (2x) button

Then using the **scroll bar** at the bottom of the wave window, **scroll** to the beginning of the waveform.

Scroll to the beginning. Move the scroll bar to this position.

Look at the waveform values. Do they match your expected value for an adder?

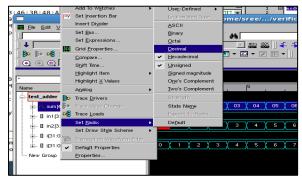

The values displayed for the bus signals (in1, in2, sum) is in hex. You can change the default radix to decimal (or binary or octal) by following this step:

Select the signal "sum". Right click on it, and select Set Radix - Decimal.

Repeat the above steps for the signal "in1" and "in2". Check the output value to see if its correct - it should be.

Next we will see how to use source code tracing. That is to see your code execution sequence. Arrange the windows so that you are able to see both of them, some overlap is fine.

Make sure you are able to see both windows.

On the main DVE gui, **click** on **Simulator - Start/Continue**. This brings the simulator back to time 0, the starting point. Notice that the waveform has cleared. Look at the source code window. Lets see what the execution sequence of your code is. Click on the **Next** button a few times:

The **yellow arrow** on the source code shows the current execution line. At the same notice that the waveform appears on the wave window. You may want to zoom in.

Continue clicking the Next button a few more times - do you see the sequence of your code execution? Based on your design knowhow, you should be able to deduce if the execution is correct - in this case it's correct. You can hit the Run button (the down arrow) to complete the simulation run.

This is how you verify a simple design. More complex designs will require advance verification techniques such as using assertions and native testbench constructs.

Now exit the simulator, Left click on File, then choose Exit and followed by OK.

This completes Task 1.

# Task 2

In this lab, you will run a basic verilog simulation using Synopsys VCS. This simulation exercise will use VCS's shell (command line) interface. The same design from Task 1 is used here.

Go to directory task2

# cd ~/lab\_work/verification/task2

Use the "Is" command to view the files in this directory. You should find two files: adder.v (design file) and test\_adder.v (testbench file)

Check the adder file for syntax errors. Type:

#### vcs adder.v

Did the design compile successfully?

VCS returns an error message like this:

```

Parsing design file 'adder.v'

Error-[SE] Syntax error

Following verilog source has syntax error :

"adder.v", 4: token is '['

ouput [4:0] sum;

1 error

CPU time: .105 seconds to compile

```

This indicates a syntax error in your adder source file. The message **"adder.v", 4:** indicates the file and line number where the error might have occurred. In general, the error might occur on the specified line or one line above. Can you tell what the error is?\_\_\_\_\_

The word "output" is spelt wrongly. It should be "output" and not "ouput".

Open the file, adder.v in a text editor (gedit), type:

# gedit adder.v

Fix the error and save the file. Exit gedit when done.

Now recompile the design again:

#### vcs adder.v

The compilation should complete successfully with the message:

# ../simv up to date

Now check the testbench file:

#### vcs test\_adder.v adder.v

Seems like more errors are detected. You should get the following message:

```

Error-[IBLHS-NRIRT] Illegal behavioral left hand side

test_adder.v, 15

Non reg/integer/real/time/realtime cannot be used on the left hand side of

this assignment

The offending expression is : in1

Source info: in1 = i;

Error-[IBLHS-NRIRT] Illegal behavioral left hand side

test_adder.v, 16

Non reg/integer/real/time/realtime cannot be used on the left hand side of

this assignment

The offending expression is : in2

Source info: in2 = j;

2 errors

```

The cause of this error is the testbench file, **test\_adder.v**. Based on your knowledge of **verilog**, fix this error using the same method as above, then recompile the design.

Do not continue until you have fixed all errors, and compilation completes successfully.

The testbench contains self-checking constructs. Run the simulation using the command shell:

#### vcs test\_adder.v adder.v -R -l run.log

The option "-I" thats small "L", captures all the output to a log (text file) called run.log. Once simulation completes, use gedit to open the run.log file:

#### gedit run.log

Browse through the file. Are the results correct? \_\_\_\_\_\_. It should be. Notice the message "Simulation Completed Successfully". This is the message from the testbench indicating that the simulation run has completed with no functional errors i.e. NO BUGS!

Now we will create a functional error in the design adder. Functional errors are caught during simulation run, and the cause of the error is found during debug. Syntax errors are found during compilation.

Our design is an adder, buts let change the function to that of a subtractor. In the file, adder.v, change the "+" to a "-" sign:

from: assign sum = in1 + in2;

to: assign sum = in1 - in2;

Use **gedit** to make the above change and **save** the file. Now rerun the simulation:

## vcs test\_adder.v adder.v -R -I run.log

Once the simulation completes, open the log file, run.log with gedit, and look at the output. Notice all the error messages:

The above is a simple example of a self-checking testbench. Self-checking testbench is a better way to verify complex designs.

In this lab, you have seen how to fix syntax error and run the simulation using the shell (no GUI) by using self-checking testbench.

This completes VCS lab.

# Design Compiler (DC) Synthesis Lab

# Task 1

In this lab you will perform logic synthesis operation on a Verilog source code using Synopsys Design Compiler (DC). Logic synthesis optimizes and converts your RTL design into a Gate-level netlist.

Go to directory task1 under the lab\_work/synthesis/task1 directory:

# cd ~/lab\_work/synthesis/task1

List down all the directories/files under the current directory:

ls

The directory **lib** contains the standard cell technology library required for synthesis. The **source** directory contains the Verilog source files that will be synthesized. Note that for synthesis, we don't require the testbench.

# 1. DC Setup

Before we can start using DC, we will need to create a setup file that specifies the standard cell library that we are going to use and its location. Using gedit, create a file called ".synopsys\_dc.setup" (note: there is a "." at the beginning of the file name).

# gedit .synopsys\_dc.setup

Add the following library settings to the file:

set search\_path "\$search\_path ./lib" set target\_library "saed90nm\_max\_pg.db" set link\_library " \* \$target\_library" set symbol\_library "generic.sdb"

Save the ".synopsys\_dc.setup" and exit gedit.

#### 2. Read & Link Design

Launch the DC GUI, Design Vision (DV), at the terminal type:

#### design\_vision

Locate the DV command prompt at the bottom of the DV window:

|                | Opuons. |

|----------------|---------|

| design_vision> |         |

Here you can type in any DC commands. We will now verify that your library settings in the ".synopsys\_dc.setup" file was applied correctly. Type:

#### printvar search\_path

This will print to the screen all the search path that DC will look into to find files and libraries. Ignore the first few paths - they are the system wide default path which you should not modify. Look towards the end - do you see the library path: **./lib** ? If yes, proceed to the next step, else quit DV (File - Exit - OK), and change the search\_path setting in the ".synopsys\_dc.setup" file as per the specification in "1. DC Setup".

Type:

```

printvar target_library

```

You should get:

target\_library = "saed90nm\_max\_pg.db"

if you did not get the above setting, quit DV (File - Exit - OK), and change the target\_library setting in the ".synopsys\_dc.setup" file as per the specification in "1. DC Setup".

Туре

#### printvar link\_library

You should get: link\_library = " \* saed90nm\_max\_pg.db"

if you did not get the above setting, quit DV (File - Exit - OK), and change the link\_library setting in the ".synopsys\_dc.setup" file as per the specification in "1. DC Setup".

Finally type:

# printvar symbol\_library

You should get:

symbol\_library = "generic.sdb"

if you did not get the above setting, quit DV (File - Exit - OK), and change the symbol\_library setting in the ".synopsys\_dc.setup" file as per the specification in "1. DC Setup".

If you got the results as above, your library setting is correct, we can then proceed to read in the design. Click on the **Read** icon:

| 1 |  |

|---|--|

|---|--|

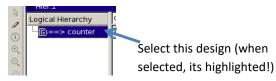

**Double Click** on the **Source** directory, and select the file, **counter.v** and then click on **Open**. This will load the RTL design into DC's memory. In the **Logical Hierarchy** pane, **select** the design, **counter**:

To view the block diagram of the design, click on the "Create Schematic of Selected Objects"

|               | <b>D0</b> |

|---------------|-----------|

| toolbar icon: |           |

You can also **right-click** on the "**counter**" design in the **Logical Hierarchy** pane and select **Schematic View**. Press the "**F**" key to zoom fit the view or use the zoon icons on the toolbar. This will show the block diagram, with the input ports on the left, and output ports on the right. Can you identify the 4 input and one output port?

| $\rightarrow$ | clk                         |  |

|---------------|-----------------------------|--|

| $\rightarrow$ | rst counter 4_pins(cout[],) |  |

| $\rightarrow$ | en                          |  |

| $\rightarrow$ | 4_pins(load[],)             |  |

What is the size (number of bits) of the output port?\_\_\_

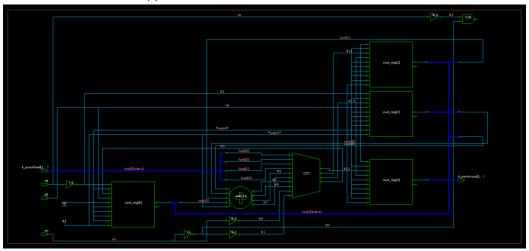

You can also get the schematic view of the RTL code – double click on the Block Diagram view of the Counter design

This is view of the unmapped RTL netlist:

#### 3. Design Constraints

Next step is to apply design constraints. For this design we will apply the following sets of constraints:

- 1. Get the smallest possible design

- 2. Clock period of 5ns

- 3. Clock transition of 0.5ns

- 4. Input delay of 1ns

- 5. Output delay of 1ns

- 6. Output load of 0.001pf

- 7. Input transition (for all inputs except clock): 0.8ns

The constraints are written using TCL syntax. Type the following in DV command prompt:

set\_max\_area 0 create\_clock -period 5 [get\_port clk] set\_clock\_transition 0.5 [get\_clock clk] set\_input\_delay 1 -clock clk [get\_port "rst en load"] set\_output\_delay 1 -clock clk [get\_port cout] set\_load 0.001 [get\_port cout] set\_input\_transition 0.8 [get\_port "rst en load"]

When you type in any of the above command, DV will return a value of "1" like this:

```

design_vision> set_max_area 0

1

design_vision> create_clock -period 5 [get_port clk]

1 ______

design_vision> set_clock_transition 0.5 [get_clock clk]

1

```

A return value of "1" indicates the command as has been successfully accepted by DC. If you make any mistakes, just retype the command again.

Next step is to optimize the design.

# 4. Optimize Design

We will now optimize and map the design to cells from the target library. To do that, **click** on **Design - Compile Design - Ok**. Do not change any setting in the dialog box.

Wait until optimization completes. You will get the following message in DV's log window:

| _        |               |              |              | _           | _          |             | _         | <br> |

|----------|---------------|--------------|--------------|-------------|------------|-------------|-----------|------|

| -        | 0:00:02       | 244.0        |              | 0.0         | 0.0        |             |           |      |

| Loa      | ading db file | e '/home/sre | ee/lab_work/ | synthes is, | /task1/lib | /saed90nm_m | ax_pg.db' |      |

|          |               |              |              |             |            |             |           |      |

| c        | Optimization  | Complete     |              |             |            |             |           |      |

|          |               |              |              |             |            |             |           |      |

| 1<br>doc | sign vision>  |              |              |             |            |             |           |      |

| ues      | sign_vision>  |              |              |             |            |             |           |      |

|          |               |              |              |             |            |             |           |      |

| Log      | History       |              |              |             |            |             |           |      |

|          |               |              |              |             |            |             |           |      |

| desig    | n_vision>     |              |              |             |            |             |           |      |

|          |               |              |              |             |            |             |           |      |

Notice how when the optimization completes the design hierarchy view is cleared. **Click** on **Hierarchy – New Logical Hierarchy View** to load the compiled (mapped) design.

Take a look at the design schematic again. **Right Click** on **counter** design under the Logical Hierarchy pane and choose **Schematic View**. **Double click** on the Block View to get the Schematic View. Notice how the schematic view has changed. The design is now composed of gates from your target library.

#### 5. Save the Design

Once optimization has completed, we can save the design and other related data for the next stage in the IC design process (layout).

To save the netlist as binary (DDC) file, at DV command prompt, type:

```

write -f ddc -hierarchy -out ./netlist/counter.ddc

```

To save a Verilog netlist, type:

#### write -f verilog -hierarchy -out ./netlist/counter.v

We also need to write out our design constraints in a format called SDC:

#### write\_sdc ./netlist/counter.sdc

Now we need to analyze the design to see if we have met our design constraints (area & timing). For that we need to generate reports.

# 6. Analyze Design

To get the area of your design, type: report\_area

Take a look at the last two lines:

Total cell area: 236.838003

Total area: 244.004085

The total area includes the cell and wire(net) area. The numbers for your design **might vary** slightly!

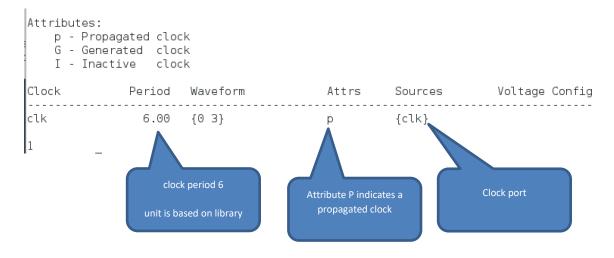

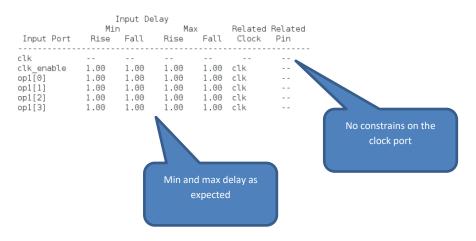

To get a clock report, type: **report\_clock**

What is the clock period? \_\_\_\_\_

Does it match your design constrain? \_\_\_\_\_. It should!

Type: report\_clock -skew

What is the clock transition? \_\_\_\_\_\_. It should!

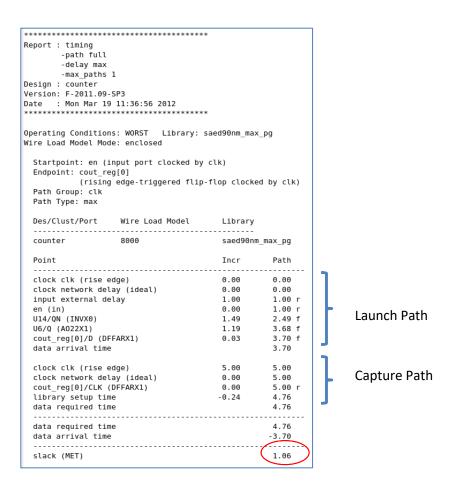

Generate a timing report, type: report\_timing

You will get the following report:

Take a look at the slack value. Your number maybe slightly different from the above (1.06). However it should be a positive value. A positive slack value (MET) indicates that you have met your timing constraints. A negative slack value (VIOLATED) indicates a timing constraint failure. A timing failure will require re-optimizing the design or changing the source code.

Quit DV, click on File - Exit - OK.

This completes task 1. Proceed to the next task.

#### Task 2

In this lab, you will perform synthesis using DC shell interface i.e. the most common way of doing synthesis. You will create a script file containing all the design constraints and another command script file to run the synthesis process in batch mode.

Perform all task under the task2 directory:

# cd ~/lab\_work/synthesis/task2

The ".synopsys\_dc.setup" has already been created with the necessary library and path settings. To run in batch mode, we will need two files - constraints and command file. Lets create the constraints file first. Type the following:

#### gedit scripts/constraints.tcl

Add in the following constraints to the script file:

```

set_max_area 0

create_clock -period 5 [get_ports clk]

set_clock_transition 0.5 [get_clocks clk]

set_input_delay 1 -clock clk [get_ports "rst en load"]

set_output_delay 1 -clock clk [get_ports cout]

set_load 0.001 [get_ports cout]

set_input_transition 0.8 [get_ports "rst en load"]

```

These are similar constraints to task 1. **Save** the file and **exit gedit**. The file will be saved to the **scripts** directory. Check to see if the file has any syntax errors, at terminal, type:

#### dcprocheck scripts/constraints.tcl

If you get any errors, its due to typos, refer to the above constraints, and fix the errors. Make sure you get no errors before proceeding to the next step. If there are no errors, dcprocheck will return the following message:

```

Loading snps_tcl.pcx...

Loading syn.pcx...

scanning: /home/sree/lab_work/synthesis/task2/scripts/constraints.tcl

checking: /home/sree/lab_work/synthesis/task2/scripts/constraints.tcl

```

Now create a command file, which will read in the design, apply the constraints, compile the design, generate reports and exit the tool.

#### gedit scripts/run.tcl

(you can use gedit or any text editor of your choice)

Add in the following commands to the script file:

```

read_verilog source/counter.v

link

source scripts/constraints.tcl

compile

write -f ddc -hierarchy -out netlist/counter.ddc

write -f Verilog -hierarchy -out netlist/counter.v

write_sdc netlist/counter.sdc

redirect -file reports/area.rpt { report_area }

redirect -file reports/timing.rpt { report_timing }

redirect -file reports/clock.rpt { report_clock }

redirect -file -append reports/clock.rpt { report_clock -skew }

exit

```

**Save** the file and **exit gedit**. The file will be saved to the **scripts** directory. Check to see if the file has any syntax errors, at terminal, type:

# dcprocheck scripts/run.tcl

Script commands summary:

- read\_verilog/link: Read in the design, and checks to ensure design is loaded properly

- source: read in constraints file, and applies the constraints to the current design

- compile: optimizes and maps the design to the target technology

- write: saves design netlist

- write\_sdc: saves design constraints file (SDC)

- redirect -file: redirects the specific command output to a file instead of the screen.

Now run the synthesis process in batch mode, type:

dc\_shell -f scripts/run.tcl |tee dc.log

Note: | is the pipe character (typically above the return/enter key).

The above command will invoke dc\_shell, which is the shell interface program for DC, and execute the commands in the file run.tcl. All the output to screen is also captured in the log file dc.log.

Once the synthesis process completes, use gedit to view the file, dc.log:

# gedit dc.log

Check to see if log contains any "Error". If you have, fix it - its probably caused by typos.

Then use **gedit** to view all the report files in the **reports** directory.

What is the total area: \_\_\_\_\_

What is the clock transition time? \_\_\_\_\_\_

Is the timing slack positive or negative?

Did you meet your timing constraints? \_\_\_\_\_

This completes task 2. Continue to the next task.

#### Task 3

In this task, you will have to perform the synthesis task based on the given specification. You can use Design Vision or dc\_shell to perform the synthesis operation.

Following are the specifications of the design:

| Design name                  | detector               |

|------------------------------|------------------------|

| File name                    | source/detector.v      |

| Target library               | syn90nm_slow.db        |

| Link library                 | * syn90nm_slow.db      |

| Symbol library               | generic.sdb            |

| Library path                 | lib                    |

|                              |                        |

| Clock period                 | 2ns                    |

| Input delay                  | 0.2ns                  |

| Output delay                 | 0.1ns                  |

| Clock transition time        | 0.01ns                 |

| Input signal transition time | 0.1ns                  |

| Output capacitance           | 0.005pf                |

| Area goal                    | smallest possible size |

Based on the above specification, your task is to:

- Create a ".synopsys\_dc.setup" file with the appropriate library and path settings.

- Create a constraints file with the name detector\_cons.tcl.

- Create a command file with the name **run\_detector.tcl** that does the following:

- Reads in the design

- Applies the above constraints via detector\_cons.tcl

- Optimizes the design

- Generates a timing, area, *cell* and clock report which must be saved to the reports directory

- Write out a *Verilog* netlist and save it to the **netlist** directory

- Write out a DDC file and save it to the netlist directory

- Generates **SDC** file and saves it to the **netlist** directory

- Exit DC/DV when done.

- All DC run commands and outputs must be capture in a log file.

When done, you will need to hand-over the following files to your lecturer:

- .synopsys\_dc.setup

- run\_detector.tcl

- detector\_cons.tcl

- Area report

- Timing report

- Cell report

- Clock report

- Synthesis run log

Does your design meet its timing constraints? \_\_yes\_. What is the slack? \_\_0.091\_\_

This completes task 3. In the next lab, we will cover how to do layout (PnR).

Thank you

# **Physical Implementation Lab**

In this lab you will perform physical implementation operation on a netlist using Synopsys IC Compiler (ICC). Commonly called place & route (or pnr), physical implementation task takes in a gate-level netlist and converts it into a physical layout that can be sent for IC fabrication.

Go to directory task1 under the **lab\_work/pnr** directory:

# cd ~/lab\_work/pnr

List down all the directories/files under the current directory:

ls

The directory **ref** contains the standard cell technology library required by ICC. The **netlist** directory contains the gate-level netlist file (*ORC.ddc*) in **DDC** format. This file was generated by Design Compiler using the "write -f ddc …" command. Do all your work from the *pnr* directory.

# 1. ICC Setup

Before we can start using ICC, we will need to create a setup file that specifies the standard cell library that we are going to use and its location. For this lab the setup file,

".synopsys\_dc.setup" (note: there is a "." at the beginning of the file name) is provided for you. This is the same file that is used by Design Compiler but now we have additional libraries specified in it.

Using gedit, view the contents fo the ".synopsys\_dc.setup" file. DO NOT MODIFY THIS FILE!

# gedit .synopsys\_dc.setup

Browse through the file to view the physical library i.e. Milkyway settings. When done, **exit** gedit.

#### 2. Read Design

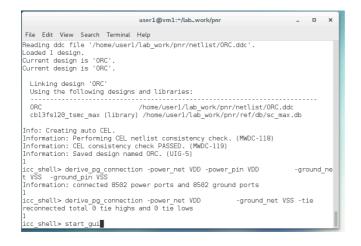

Launch ICC in shell mode, open a terminal and type:

cd ~/lab\_work/pnr icc\_shell

At the ICC command prompt, read in the DDC netlist from the netlist directory, type:

#### import\_design -format ddc -top ORC ./netlist/ORC.ddc

Next, tie all the power pins of the gates in the netlist to the power nets, VDD and VSS:

derive\_pg\_connection -power\_net VDD -power\_pin VDD -ground\_net VSS -ground\_pin VSS derive\_pg\_connection -power\_net VDD -ground\_net VSS -tie

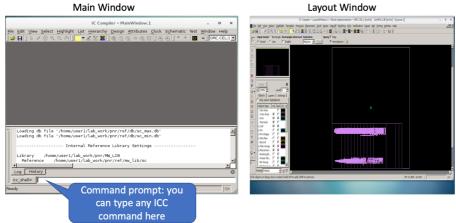

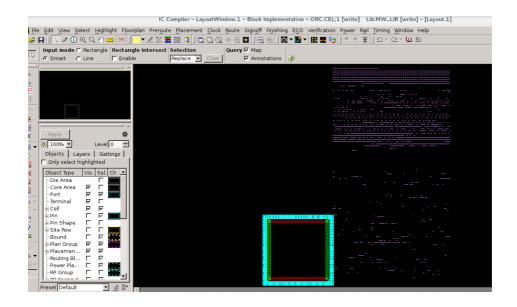

For the next step, we will use the GUI, at the ICC prompt, type: start\_gui

You will get the ICC GUI. There will be two windows – ICC Main window and Layout window.

You will do your work from the Layout window. Make that window the active window on your desktop.

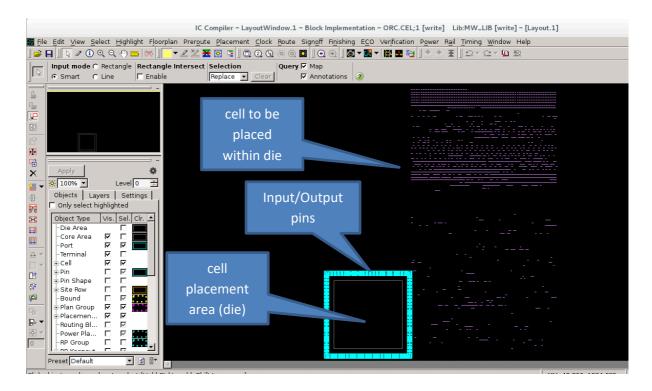

# 3. Floorplan

Next up is floorplan. Here is where we specify the die area, pin arrangement and power network.

From the Layout window menu bar, **Click Floorplan – Create Floorplan**. Specify the values as shown in the image below:

| ,                                | - ×                 |                          |         |

|----------------------------------|---------------------|--------------------------|---------|

| Control type                     |                     |                          |         |

|                                  | oundary             | C <u>W</u> idth/Height   |         |

| Core <u>u</u> tilization: 0.7    |                     | Core wi <u>d</u> th: 1.0 |         |

| Asp <u>e</u> ct ratio (H/W): 1.0 |                     | Core <u>h</u> eight: 1.0 |         |

| 🔽 Horizontal row 🖉 🛛             | D <u>o</u> uble bac | :k                       |         |

|                                  | lip first rov       | N                        |         |

| Space between core area          | a and term          | ninals (pads) —          |         |

| <u>L</u> eft: 50                 | <u> </u>            | ght: 50                  |         |

| Bottom: 50                       | <u>T</u> o          | p: 50                    |         |

| 📕 Keep macro place               | Keep sto            | <del>i cell pla</del> ce |         |

| <u>Г M</u> in pad height I       | Pad <u>l</u> imit   | t                        |         |

| ☐ Keep I/O placement             |                     |                          |         |

| OK Cancel                        | <u>A</u> pply       | Default <u>H</u> e       | elp 📕 🔫 |

|                                  |                     |                          |         |

Click OK.

Your Layout window will look similar to this:

Before we can move all the cells in, we need to create the power (VDD) and ground (VSS) rings (supply network). Click **Preroute – Create Rings**. Key in the values as shown in the image below:

| Rectilinear Rectangular     Nets: VDD VSS     Around     © gore     Specified macros     Specified macros<                                                                                                                |          | ,g                        |                  |              | Create Rin             | gs                 |                 | _ ×    | : |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------------------|------------------|--------------|------------------------|--------------------|-----------------|--------|---|

| Around<br>© Core<br>© Specified macros © Specified as a Group © Except macros<br>Macros:<br>© Begion<br>Coordinates<br>© Coordinates<br>© Offset Width Layer<br>© METAL4 (26) © Bottom © Top<br>© Bottom 1 20 © METAL3 (22) © Coordinates<br>© Offsets applied for DRC spacing<br>© Create innermost core ring conservatively<br>© Use advanced via rules                                                                                                                                            | t<br>a [ | Rectilinear               | Rectangul        | ar           |                        |                    |                 |        |   |

| <ul> <li>Gore</li> <li>Specified macros  <ul> <li>Specified macros</li> <li>Specified as a Group</li> <li>Except macros</li> </ul> </li> <li>Macros: <ul> <li>Begion</li> <li>Coordinates</li> <li>Coordinates</li> </ul> </li> <li>Side Offset Width Layer Extend <ul> <li>Extend</li> <li>Extend</li> <li>Extend</li> <li>Extend</li> </ul> </li> <li>Side Offset Width Layer Extend <ul> <li>METAL4 (26)</li> <li>Bottom Top</li> <li>Right 1</li> <li>20</li> <li>METAL4 (26)</li> <li>Bottom Top</li> <li>Bottom 1</li> <li>20</li> <li>METAL4 (26)</li> <li>Extend</li> <li>Fop</li> <li>1</li> <li>20</li> <li>METAL3 (22)</li> <li>Left Right</li> <li>Coeffsets applied for DRC spacing</li> </ul> </li> <li>Ignore parallel targets <ul> <li>Create innermost core ring conservatively</li> <li>Use advanced via rules</li> </ul> </li> </ul>                                                                                                                                                                            |          | Nets: VDD \               | /ss              |              |                        |                    |                 | B 6 B  |   |

| <ul> <li>Coordinates</li> <li>Coordinates</li> <li>Side Offset Width Layer Extend</li> <li>Coordinates</li> <li>Create innermost core ring conservatively</li> <li>Use advanced via rules</li> </ul> |          | Around                    |                  |              |                        |                    |                 |        |   |

| Macros:<br>Region<br>Coordinates<br>Side Offset Width Layer Extend<br>Left 1 20 METAL4 (26) Bottom Top<br>Right 1 20 METAL4 (26) Bottom Top<br>Right 1 20 METAL3 (22) Ceft Right<br>Top 1 20 METAL3 (22) Ceft Right<br>Coffsets applied for DRC spacing<br>Ignore parallel targets<br>Create innermost core ring conservatively<br>Use advanced via rules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          | ⊙ <u>C</u> ore            |                  |              |                        |                    |                 |        | L |

| Coordinates         Coordinates         Side       Offset         Width       Layer         Extend         <                                                                                                                                                                                                                                                  |          | C <u>S</u> pecified       | macros           | O Specifi    | ied as a <u>G</u> roup | C <u>E</u> xcept m | nacros          |        |   |

| Coordinates<br>Coordinates<br>Side Offset Width Layer Extend<br>✓ Left 1 20 ✓ METAL4 (26) ✓ Bottom Top<br>✓ Right 1 20 ✓ METAL4 (26) ✓ Bottom Top<br>✓ Bottom 1 20 ✓ METAL3 (22) ✓ Left ⊂ Right<br>✓ Top 1 20 ✓ METAL3 (22) ✓ Left ⊂ Right<br>✓ Offsets applied for DRC spacing<br>✓ Ignore parallel targets<br>⊂ Create innermost core ring conservatively<br>⊂ Use advanced via rules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          | Macros:                   |                  |              |                        |                    |                 |        |   |

| Side Offset Width Layer Extend<br>Left 1 20 METAL4 (26) Bottom Top<br>Right 1 20 METAL4 (26) Hottom Top<br>Bottom 1 20 METAL3 (22) Ceft Right<br>Top 1 20 METAL3 (22) Left Right<br>Coffsets applied for DRC spacing<br>Ignore parallel targets<br>Create innermost core ring conservatively<br>Use advanced via rules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |                           |                  |              |                        |                    | <u>[</u>        |        |   |

| Side Offset Width Layer Extend<br>Left 1 20 METAL4 (26) Bottom Top<br>Right 1 20 METAL4 (26) Ebottom Top<br>Bottom 1 20 METAL3 (22) Left Right<br>Top 1 20 METAL3 (22) Left Right<br>C Absolute offset<br>Offsets applied for DRC spacing<br>Ignore parallel targets<br>Create innermost core ring conservatively<br>Use advanced via rules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |                           | otos ——          |              |                        |                    |                 |        |   |

| <ul> <li>Left 1 20 METAL4 (26) Bottom Top</li> <li>Right 1 20 METAL4 (26) Eottom Top</li> <li>Bottom 1 20 METAL3 (22) Cleft Right</li> <li>Top 1 20 METAL3 (22) Cleft Right</li> <li>C Absolute offset</li> <li>Offsets applied for DRC spacing</li> <li>Ignore parallel targets</li> <li>Create innermost core ring conservatively</li> <li>Use advanced via rules</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |                           | ates             |              |                        |                    |                 |        |   |

| <ul> <li>Left 1 20 METAL4 (26) Bottom Top</li> <li>Right 1 20 METAL4 (26) Eottom Top</li> <li>Bottom 1 20 METAL3 (22) Feft Right</li> <li>Top 1 20 METAL3 (22) Left Right</li> <li>C Absolute offset</li> <li>Offsets applied for DRC spacing</li> <li>Ignore parallel targets</li> <li>Create innermost core ring conservatively</li> <li>Use advanced via rules</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3        |                           |                  |              |                        | 1                  |                 |        |   |

| <ul> <li>Right 1 20 METAL4 (26) Eottom Top</li> <li>Bottom 1 20 METAL3 (22) Ceft Right</li> <li>Top 1 20 METAL3 (22) Cleft Right</li> <li>Absolute offset</li> <li>Offsets applied for DRC spacing</li> <li>Ignore parallel targets</li> <li>Create innermost core ring conservatively</li> <li>Use advanced via rules</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |                           |                  |              |                        |                    | om 🗖 Top        |        |   |

| <ul> <li>✓ Bottom 1 20 METAL3 (22) ✓ Left Right</li> <li>✓ Top 1 20 METAL3 (22) ✓ Left Right</li> <li>○ Absolute offset</li> <li>○ Offsets applied for DRC spacing</li> <li>☐ Ignore parallel targets</li> <li>☐ Create innermost core ring conservatively</li> <li>☐ Use advanced via rules</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1        |                           |                  |              |                        |                    |                 |        |   |

| <ul> <li>Top 1 20 METAL3 (22) Left □ Right</li> <li>○ Absolute offset</li> <li>○ Offsets applied for DRC spacing</li> <li>□ Ignore parallel targets</li> <li>□ Create innermost core ring conservatively</li> <li>□ Use advanced via rules</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          | _                         | <u> </u>         |              |                        |                    |                 |        |   |

| <ul> <li><u>Absolute offset</u></li> <li><u>Offsets applied for DRC spacing</u></li> <li>Ignore <u>parallel targets</u></li> <li><u>Create innermost core ring conservatively</u></li> <li><u>Use advanced via rules</u></li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |                           |                  |              |                        |                    | -               |        |   |

| <ul> <li>Offsets applied for DRC spacing</li> <li>Ignore parallel targets</li> <li>Create innermost core ring conservatively</li> <li>Use advanced via rules</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          | М Тор                     |                  |              | METAL3 (2              |                    | - Right         |        |   |

| ☐ Ignore <u>p</u> arallel targets<br>☐ Create <u>i</u> nnermost core ring conservatively<br>☐ Use a <u>d</u> vanced via rules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |                           |                  |              |                        |                    |                 |        |   |

| <ul> <li>Create innermost core ring conservatively</li> <li>Use advanced via rules</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |                           | ⊙ <u>O</u> ffset | s applied fo | or DRC spacing         |                    |                 |        |   |

| ☐ Use a <u>d</u> vanced via rules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          | └<br>□ Ignore <u>p</u> ar | allel target     | s            |                        |                    |                 |        |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          | Create inr                | nermost co       | re ring cons | servatively            |                    |                 |        |   |

| E Extend for multiple connections, for one of 0.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          | ∏ Use a <u>d</u> var      | nced via rul     | es           |                        |                    |                 |        | L |

| Extend for multiple connections for gap < 10.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          | □ Extend for              | multiple c       | onnections   | for gap < 0.0          | )                  |                 |        |   |

| i i i i i i i i i i i i i i i i i i i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Ē        |                           |                  |              |                        |                    |                 |        |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |                           |                  |              |                        |                    |                 |        |   |

| OK Cancel <u>A</u> pply <u>U</u> ndo <u>D</u> efault <u>H</u> elp ▼                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          | [                         | ок               | Cancel       | <u>A</u> pply          | <u>U</u> ndo       | <u>D</u> efault | Help 🗸 | Ī |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |                           |                  |              |                        |                    |                 |        |   |

Click OK.

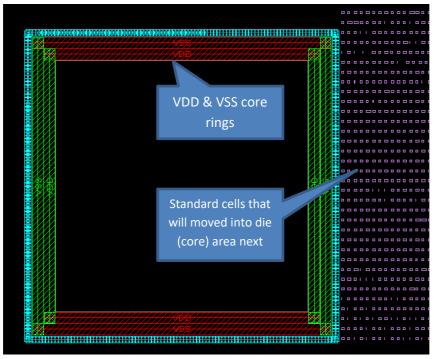

The Layout window should look like this:

Using the magnifier icon on the toolbar, zoom into the rectangle area to have a closer look.

Click on zoom in tool, and draw a rectangle around the die area to zoom in. The zoomed in view in shown below:

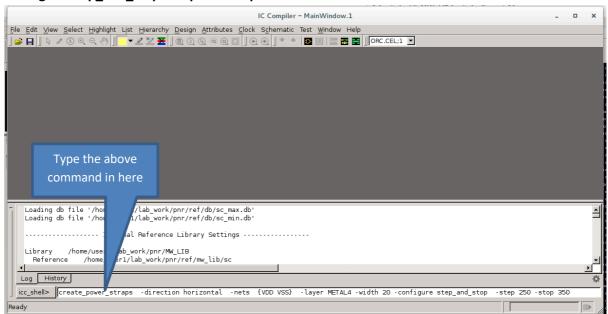

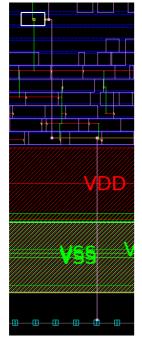

Once the rings hanve been created, we will create the power straps. Make the Main Window the active window now (bring it to the forefront). At the icc\_shell prompt, type in the following command:

create\_power\_straps -direction horizontal -nets {VDD VSS} -layer METAL4 -width 20 -configure step\_and\_stop -step 250 -stop 350

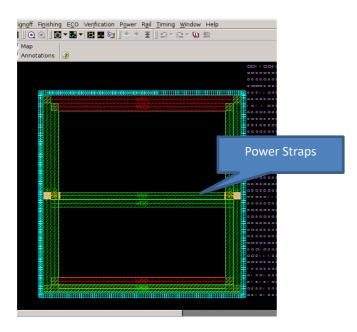

The above command will create the power straps on metal layer 4, as shown in the image below:

Back in the ICC prompt, key in the following commands:

set\_pnet\_options -complete {METAL3 METAL4}

derive\_pg\_connection -power\_net VDD -power\_pin VDD -ground\_net VSS -ground\_pin VSS

derive\_pg\_connection -power\_net VDD -ground\_net VSS -tie

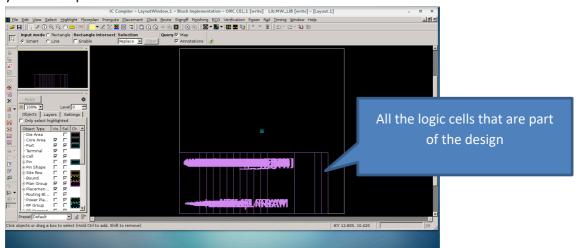

create\_fp\_placement -timing\_driven -no\_hierarchy\_gravity

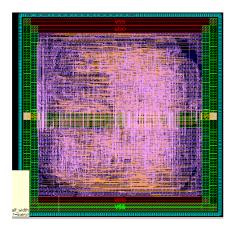

This will move all the standard cells into the core area. See figure below:

Final step under floor-planning would be to route all the power nets (VDD, VSS), type the following command:

# preroute\_standard\_cells -remove\_floating\_pieces

We are now ready for cell placement (within die) and optimization.

# 4. Placement

Lets optimize the placement of the cells within the die area, type the following commands:

set\_separate\_process\_options -placement false

place\_opt

derive\_pg\_connection -power\_net VDD -power\_pin VDD -ground\_net VSS -ground\_pin VSS derive\_pg\_connection -power\_net VDD -ground\_net VSS -tie

#### 5. Clock Tree Synthesis (CTS)

CTS builds a buffer tree for the clock network, to enable the clock signal to drive multiple flip-flops with degrading the signal strength. Type the following commands:

remove\_clock\_uncertainty [all\_clocks] clock\_opt The layout will look a little different now because of the adding in of clock buffers and routing of the clock nets. Try zoom/pan around the layout to view the clock routes. The image below shows how the clock pin is routed to a clock buffer:

# 6. Routing

Final step in the physical design process is to route the design. Type:

#### route\_opt

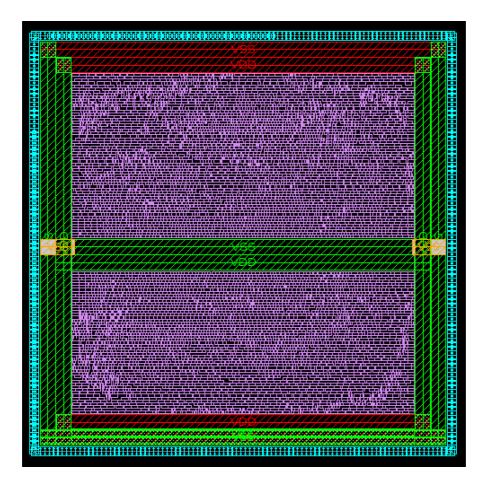

Once completed, your routed design should look like this:

Re-run the following two commands to ensure all power/ground connectivity for any new cells added in during the routing process:

derive\_pg\_connection -power\_net VDD -power\_pin VDD -ground\_net VSS -ground\_pin VSS derive\_pg\_connection -power\_net VDD -ground\_net VSS -tie

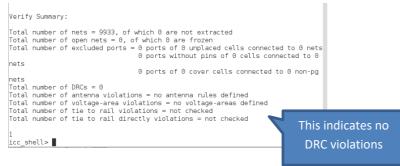

Verify the design is free of any design rule violations (DRC), type:

#### verify\_zrt\_route

#### You should get the following output:

Run a Layout vs. Schematic (LVS) check to ensure there are no shorts/open nets:

#### verify\_lvs

Now let's check if our design meets all the timing constraints. But first we need to extract the parasitic in the layout (unwanted resistance and capacitance), type:

#### extract\_rc

To run setup checks, type: report\_timing -delay max -path short

Look at the bottom of the report for the word "slack":

| clock network delay (propagated)<br>outY_reg[121]/CP (dfcrq1)<br>library setup time<br>data required time | 0.19<br>0.00<br>-0.03 | 10.19<br>10.19 r<br>10.16<br>10.16<br>10.16 |

|-----------------------------------------------------------------------------------------------------------|-----------------------|---------------------------------------------|

| data required time<br>data arrival time                                                                   |                       | 10.16<br>-10.16                             |

| slack (MET)                                                                                               |                       | 0.00                                        |

slack (MET) indicates you have met the setup timing constraints.

To run hold checks, type:

report\_timing -delay min -path short

| data required time                                     | 0.09              |  |

|--------------------------------------------------------|-------------------|--|